## CONVERSION A/N et N/A

# 3.CONVERSION ANALOGIQUE-NUMERIQUE

## 3.3 DUREE DE LA FENETRE D'ECHANTILLONNAGE SAMPLE & HOLD

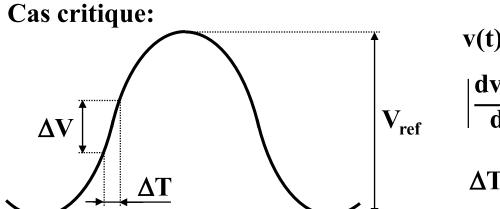

Certains convertisseurs font plusieurs fois appel au signal d'entrée  $V_{\rm in}$  en cours de conversion

La variation de  $V_{in}$  doit rester inférieure à un pas de quantification ( $V_{LSB}$ ) durant le temps de conversion  $\Delta T$

$$V_{ref} = \frac{V_{ref}}{2} \cdot \sin \omega t$$

$$V_{ref} = \frac{|\frac{dv(t)}{dt}|_{max}}{|\frac{dv(t)}{dt}|_{max}} = \frac{\omega \cdot V_{ref}}{2}$$

$$\Delta T \text{ petit } => \Delta V_{max} = \Delta T \cdot \left|\frac{dv(t)}{dt}\right|_{max}$$

$$\Delta V_{max} = \frac{V_{ref}}{2} \cdot \omega \cdot \Delta T \le V_{LSB} = \frac{V_{ref}}{2^n} \qquad \stackrel{\omega = 2\pi f}{\Longrightarrow} \Delta T \le \frac{1}{2^n \cdot \pi \cdot f}$$

## 3.3. DUREE DE LA FENETRE D'ECHANTILLONNAGE SAMPLE & HOLD

$$\Delta T \leq \frac{1}{2^n \cdot \pi \cdot f}$$

#### **EXEMPLES**

| n = 12 bits | f = 10  kHz | => | $\Delta T \le 7.8 \text{ ns}$  |

|-------------|-------------|----|--------------------------------|

| n = 8 bits  | f = 100 MHz | => | $\Delta T \le 12.4 \text{ ps}$ |

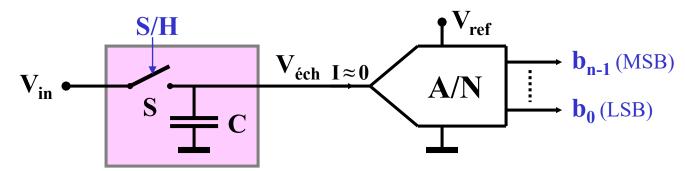

Ces exigences sur le temps de conversion  $\Delta T$  dépassent généralement les possibilités des convertisseurs actuels

#### **SOLUTION**

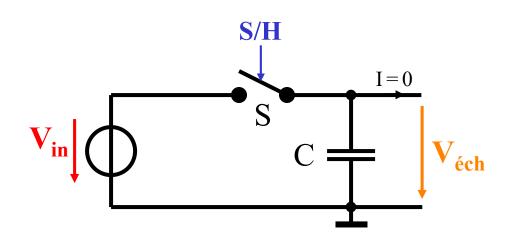

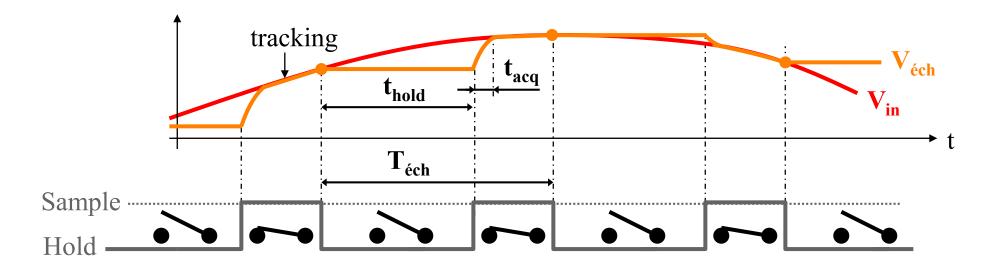

Si nécessaire, on utilise un circuit "Sample & Hold" en amont du convertisseur, afin de maintenir un signal constant à l'entrée de celui-ci durant le temps de conversion

## 3.3. DUREE DE LA FENETRE D'ECHANTILLONNAGE SAMPLE & HOLD

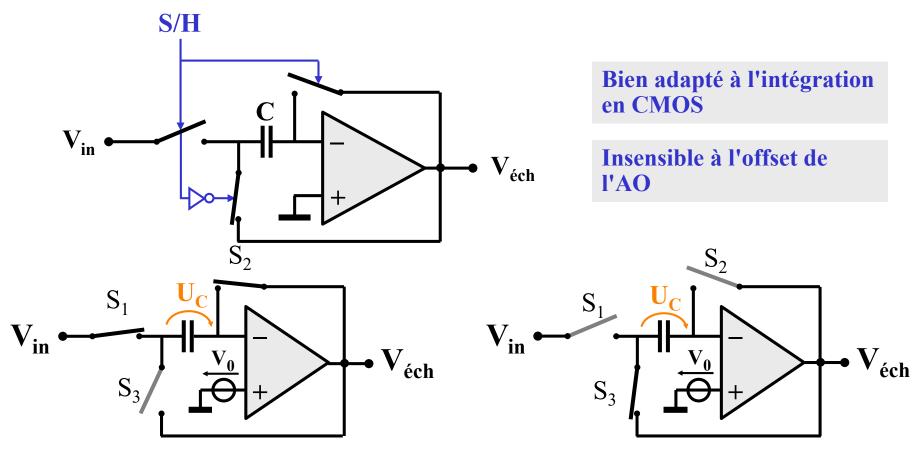

### 3.4. CIRCUITS SAMPLE & HOLD

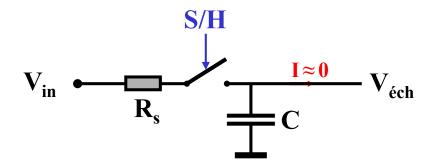

#### SAMPLE & HOLD BASIQUE

Simple et économique

Vitesse et précision limitées

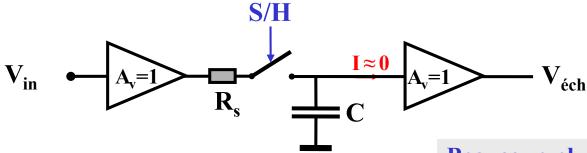

#### SAMPLE & HOLD EN BOUCLE OUVERTE AVEC BUFFERS

Beaucoup plus rapide

Meilleure précision mais encore limitée

## 3.4. CIRCUITS SAMPLE & HOLD

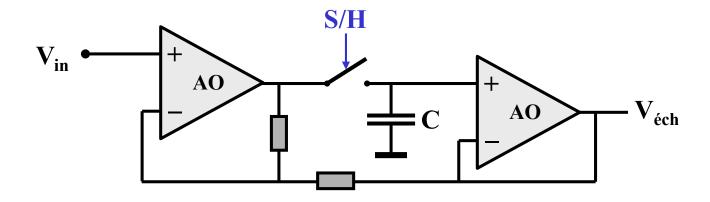

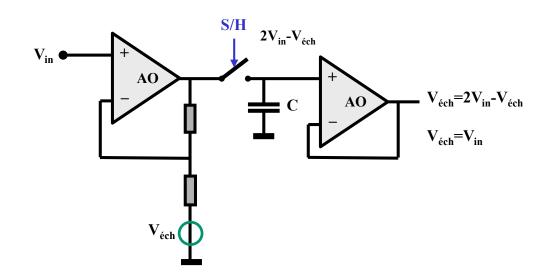

#### SAMPLE & HOLD EN BOUCLE FERMEE

#### **Rapide et precis**

### 3.2. CIRCUITS SAMPLE & HOLD

#### SAMPLE & HOLD A CAPACITE COMMUTEE

Sample:

$$V_{ech} = V_0$$

$U_C = V_{in}(t) - V_0$

Hold:

$$U_C = V_{in}(\text{ouverture } S_1) - V_0$$

$V_{ech} = V_{in}(\text{ouverture } S_1)$

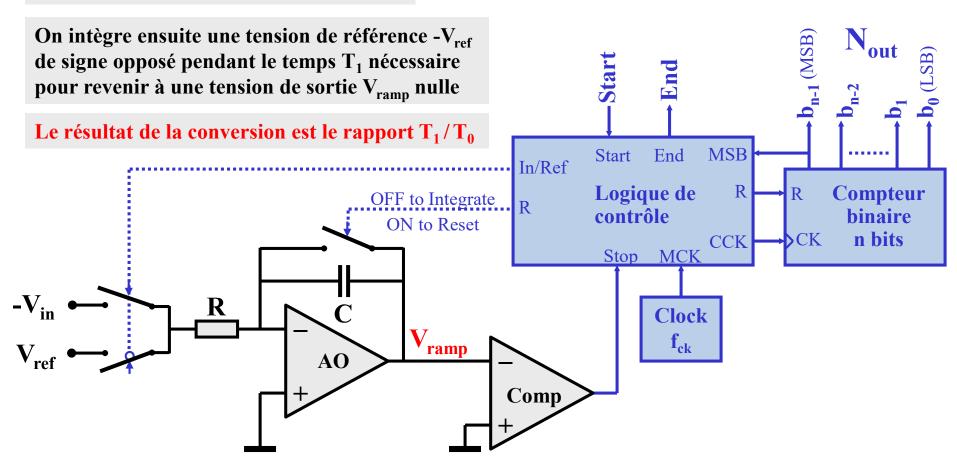

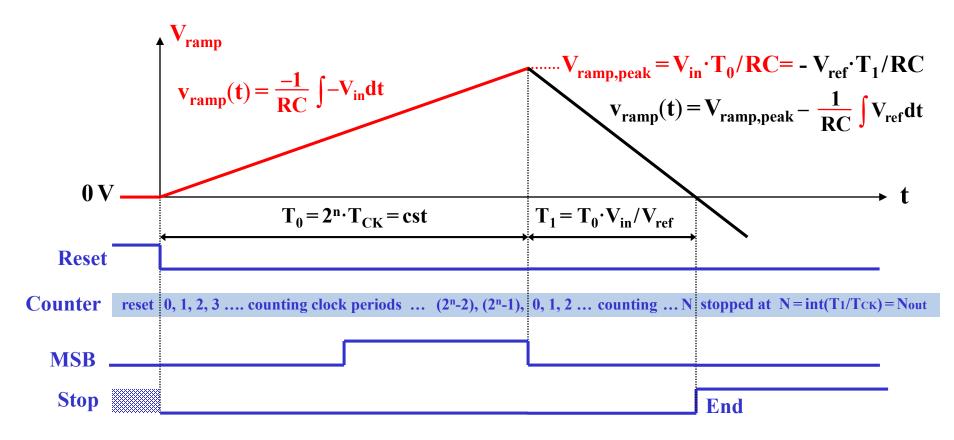

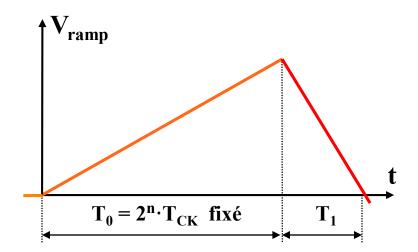

#### DOUBLE RAMPE

Principe: conversion en 2 étapes

On intègre V<sub>in</sub> pendant un temps T<sub>0</sub> fixé

$$N_{out} = entier(2^n \cdot \frac{V_{in}}{V_{ref}})$$

Insensible à l'imprécision et la sensibilité à la température des éléments R et C, et de la fréquence d'horloge.

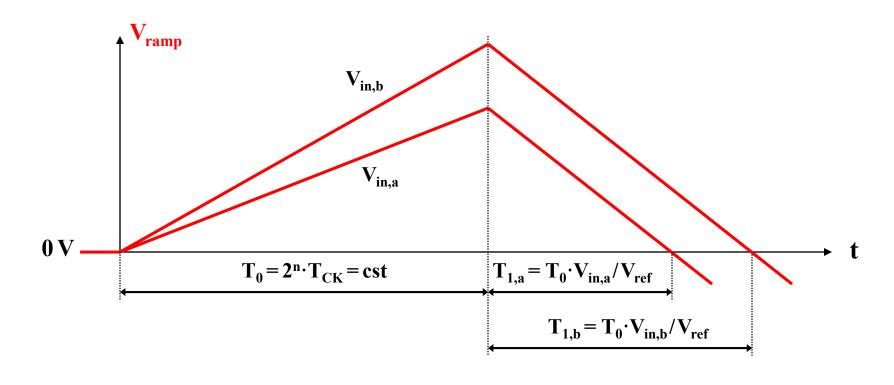

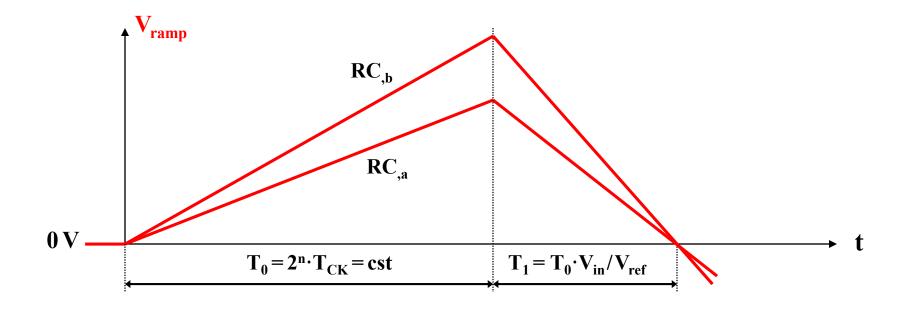

#### Effet d'une variation de V<sub>in</sub>

#### Effet d'une variation de RC à V<sub>in</sub> constante

#### · INTEGRATEUR ANALOGIQUE A DOUBLE RAMPE

- Convertisseur de haute précision (16 bits ou plus)

- Circuit simple, très bien adapté à l'intégration en technologie CMOS,

- sauf pour les éléments R et C de l'intégrateur qui sont externes

- Les limites de précision sont liées à l'offset du comparateur et de l'intégrateur.

- Ceux-ci peuvent être compensés automatiquement, jusqu'à une certaine limite, par des techniques spéciales.

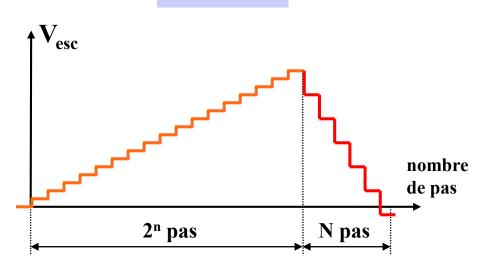

#### CONVERTISSEUR A/N INCREMENTAL

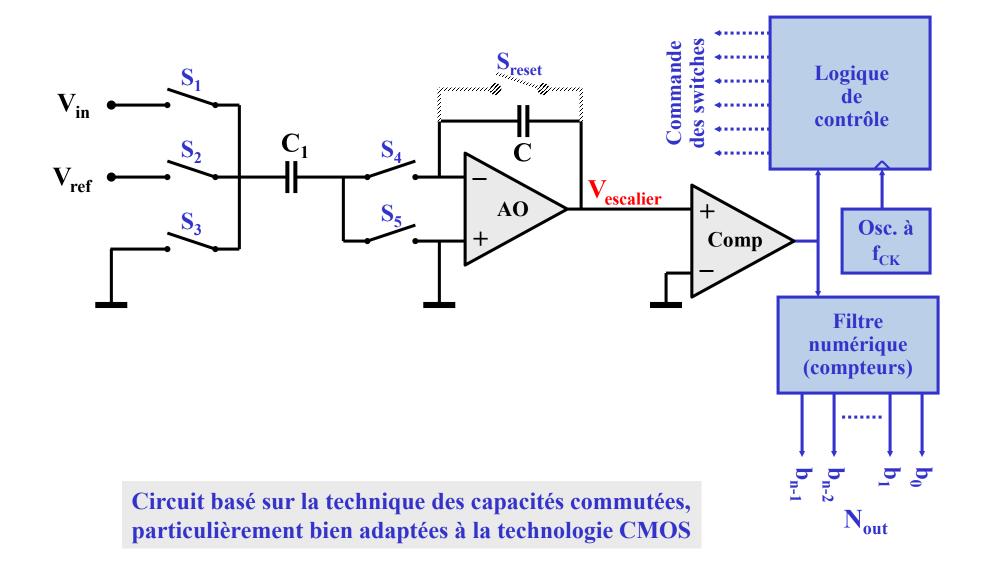

Le Convertisseur incrémental est basé sur un intégrateur à double rampe à capacité commutée, travaillant donc par pas discrets.

#### **Double rampe classique**

Intégration de  $V_{in}$ pendant un temps fixe  $T_0 = 2^n \cdot T_{CK}$  Intégration de - $V_{ref}$  durant le temps  $T_1$  nécessaire pour passer par zéro

#### Incrémental

Nombre fixe =  $2^n$  de transferts d'une charge proportionnelle à  $V_{in}$

Transferts d'une charge proportionnelle à -V<sub>ref</sub>, le nombre N de fois nécessaire pour passer par zéro

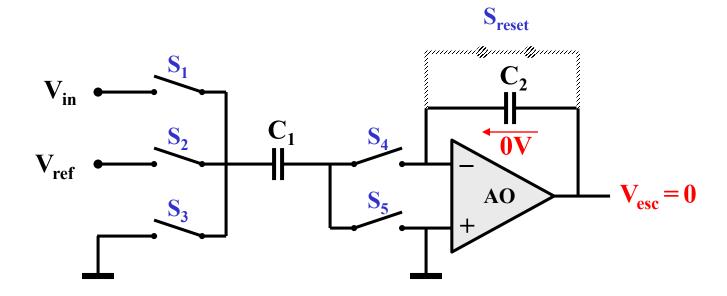

#### **Reset initial**

#### On décharge C<sub>2</sub>

Cette décharge n'est effectuée qu'une fois au début de la conversion. Le switch  $S_{reset}$  reste ensuite ouvert lors de toutes les opérations suivantes.

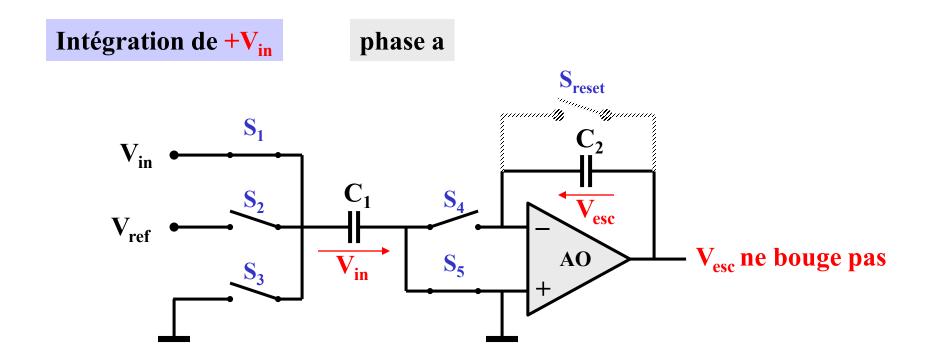

On charge  $C_1$  à  $V_{in}$ La charge de  $C_2$  ne varie pas

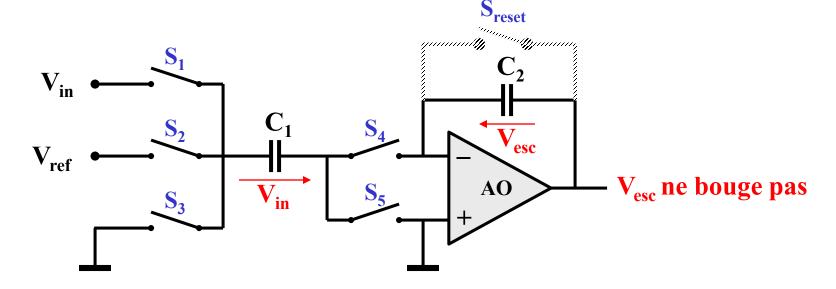

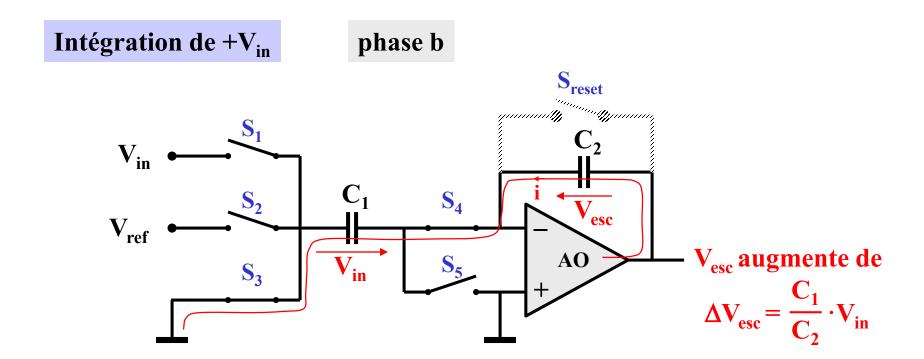

Intégration de +V<sub>in</sub>

phase intermédiaire o (open)

On ouvre tous les switches

Aucune charge n'est modifiée

C<sub>1</sub> est déchargée

Le même courant traverse C<sub>1</sub> et C<sub>2</sub> à tout instant

La charge est transférée de C<sub>1</sub> à C<sub>2</sub>.

$$\mathbf{Q} = \mathbf{C}_1 \cdot \mathbf{V}_{in} = \mathbf{C}_2 \cdot \Delta \mathbf{V}_{esc}$$

Intégration de +V<sub>in</sub>

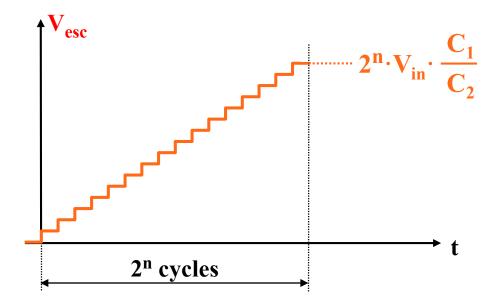

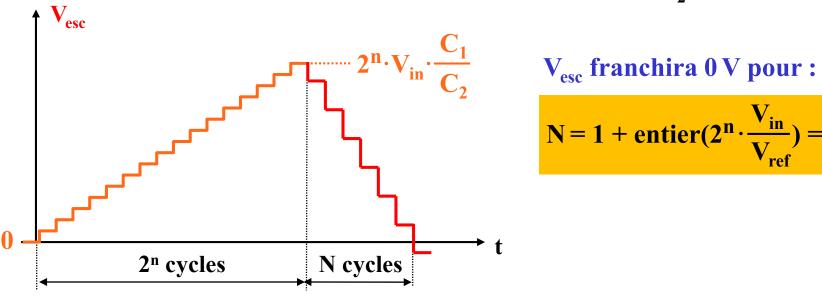

2<sup>n</sup> cycles

Après le reset, donc à partir de zéro, on effectue  $2^n$  fois le cycle d'intégration de  $+V_{ref}$  formé des phases a, o, b, o

A chaque cycle, la tension de sortie s'accroît de :  $\Delta V_{esc} = V_{in} \cdot \frac{C_1}{C_2}$

Après 2<sup>n</sup> cycles, la tension de sortie atteint le niveau :

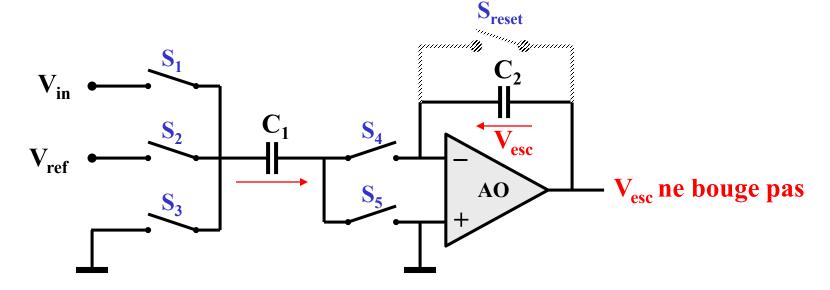

On décharge C<sub>1</sub> La charge de C<sub>2</sub> est inchangée

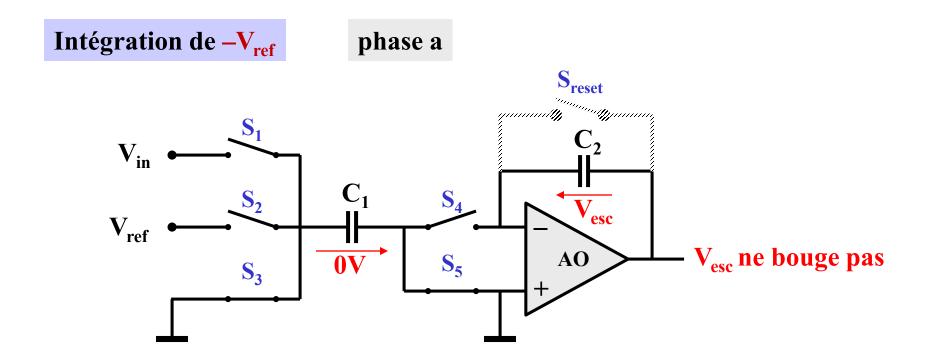

Intégration de -V<sub>ref</sub>

phase intermédiaire o (open)

On ouvre tous les switches

Aucune charge n'est modifiée

On charge C<sub>1</sub> à V<sub>ref</sub>

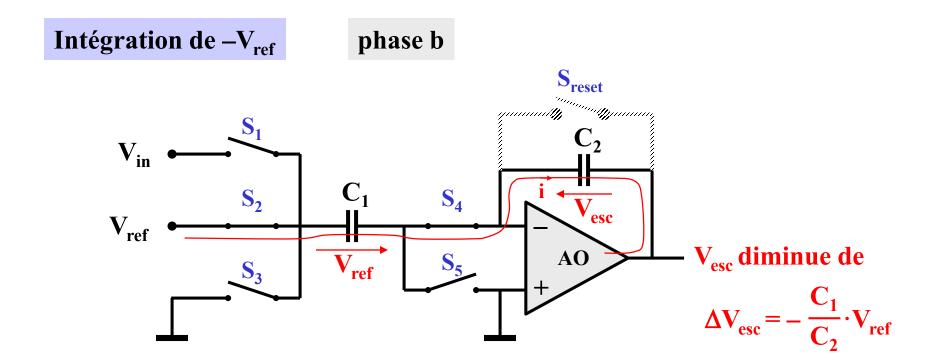

Le même courant traverse C<sub>1</sub> et C<sub>2</sub> à tout instant

La même charge est soustraite de C<sub>2</sub>

$$\mathbf{Q} = \mathbf{C}_1 \cdot \mathbf{V}_{\text{ref}} = -\mathbf{C}_2 \cdot \Delta \mathbf{V}_{\text{esc}}$$

Intégration de -V<sub>ref</sub>

**Cycles suivants**

A partir du sommet obtenu après 2<sup>n</sup> cycles d'intégration de V<sub>in</sub>, on effectue des cycles d'intégration de -V<sub>ref</sub>, chacun formé des phases a, o, b, o

A chaque cycle, la tension de sortie décroît de :

$$\Delta V_{\rm esc} = V_{\rm ref} \cdot \frac{C_1}{C_2}$$

Après N cycles, la tension de sortie est :

$$V_{esc} = 2^n \cdot V_{in} \cdot \frac{C_1}{C_2} - N \cdot V_{ref} \cdot \frac{C_1}{C_2}$$

$$N = 1 + entier(2^n \cdot \frac{V_{in}}{V_{ref}}) = N_{out}$$

#### Problème de réalisation pratique : Amplitude des signaux

Exemple:

$$V_{ref} = 5 V$$

$n = 16$

Tension de sortie maximum après  $2^n$  pas d'intégration de  $V_{in,max} = V_{ref}$ :

$$\mathbf{V}_{\text{esc,peak,max}} = 2^{\mathbf{n}} \cdot \mathbf{V}_{\text{in,max}} \cdot \frac{\mathbf{C}_1}{\mathbf{C}_2} = 2^{\mathbf{n}} \cdot \mathbf{V}_{\text{ref}} \cdot \frac{\mathbf{C}_1}{\mathbf{C}_2} = \frac{\mathbf{C}_1}{\mathbf{C}_2} \cdot 327'680 \, \mathbf{V}$$

Le rapport  $C_1/C_2$  ne peut pas être trop petit, sous peine de tomber dans la limite du bruit lors du transfert de charge avec  $V_{in,min} = V_{LSB} = V_{ref}/2^n$

$$\Delta V_{\text{esc,min}} = V_{\text{in,min}} \cdot \frac{C_1}{C_2} = \frac{V_{\text{ref}}}{2^n} \cdot \frac{C_1}{C_2} = \frac{C_1}{C_2} \cdot 76 \ \mu\text{V}$$

#### Réalisation pratique: Solution

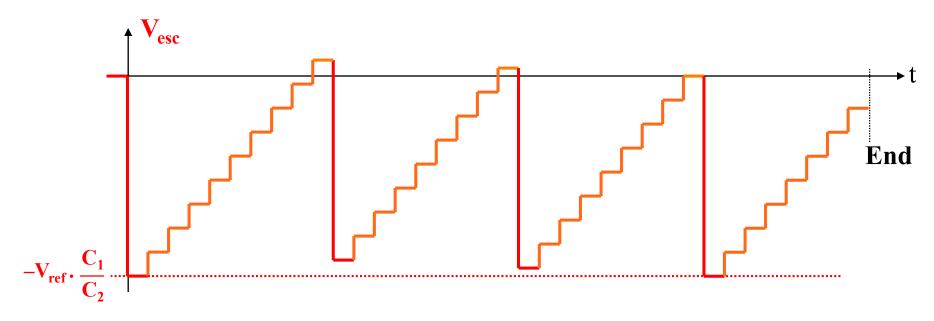

Le problème peut être résolu en entrelaçant l'intégration de V<sub>in</sub> et de (-V<sub>ref</sub>)

- 1. Un pas unique d'intégration unique de (-V<sub>ref</sub>)

- 2. Succession de pas d'intégration de  $V_{in}$ , jusqu'à croiser 0 V Retour en 1.

Le processus s'arrête lorsqu'on a dénombré un total de  $2^n$  pas d'intégration de  $V_{in}$ . A ce moment, le nombre N de pas d'intégration de  $(-V_{ref})$  effectués est le résultat.

- Convertisseur de haute précision (16 bits ou plus, sans aucun ajustage)

- · Circuit simple, très bien adapté à la technologie CMOS

- La précision est indépendante du rapport  $C_1/C_2$

- Les limites de précision sont liées à l'offset de l'AO et du comparateur, ainsi qu'à l'injection de charge des interrupteurs MOS.

- · Ces effets peuvent être compensés, jusqu'à une certaine limite, par des techniques spéciales.

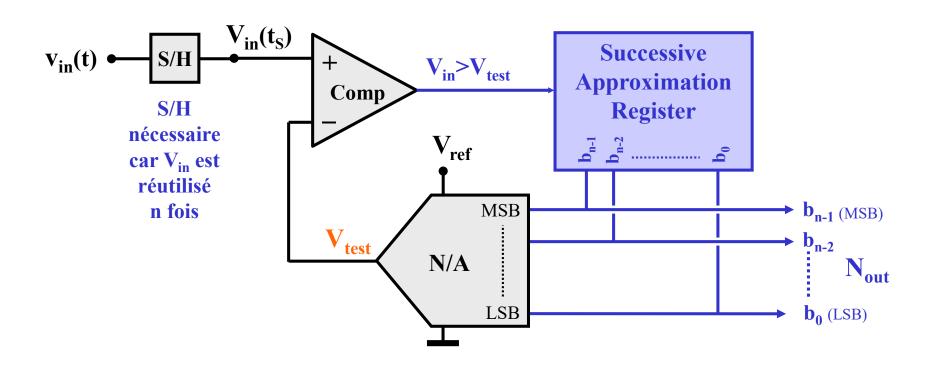

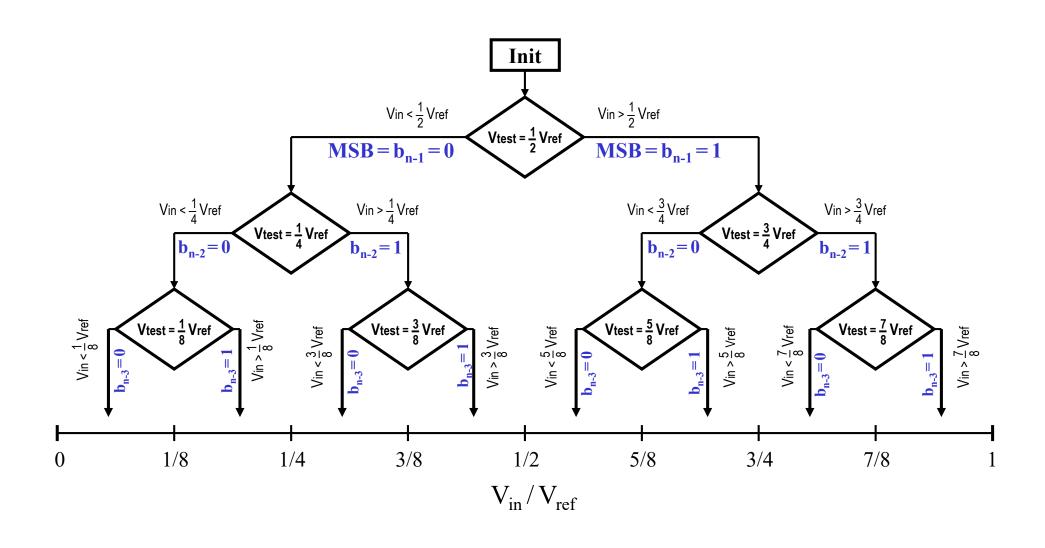

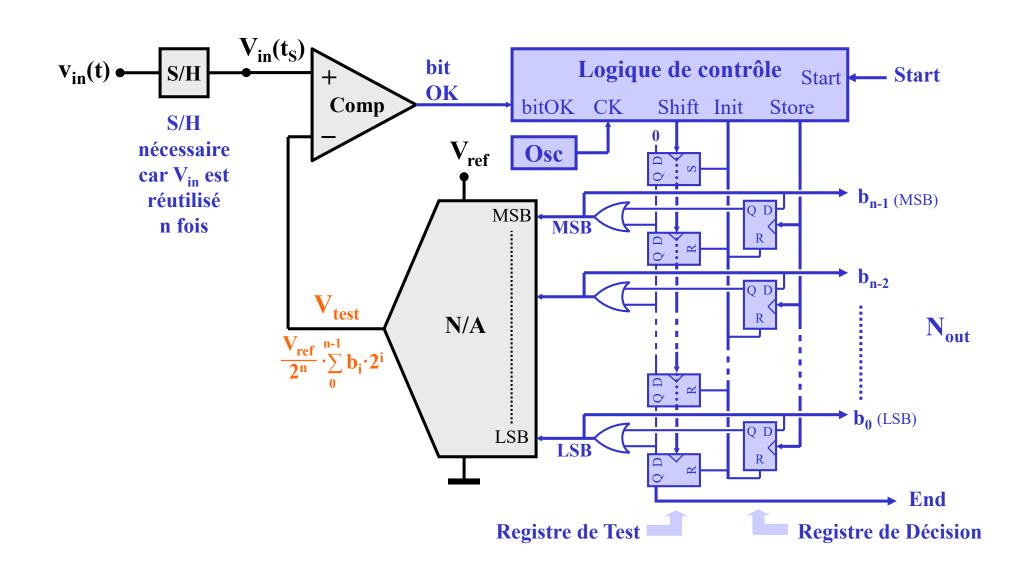

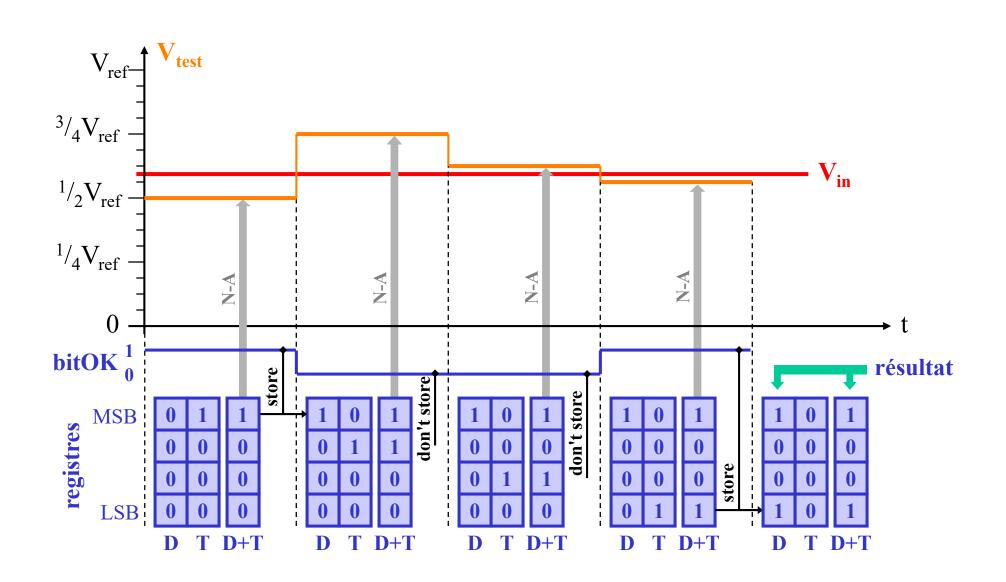

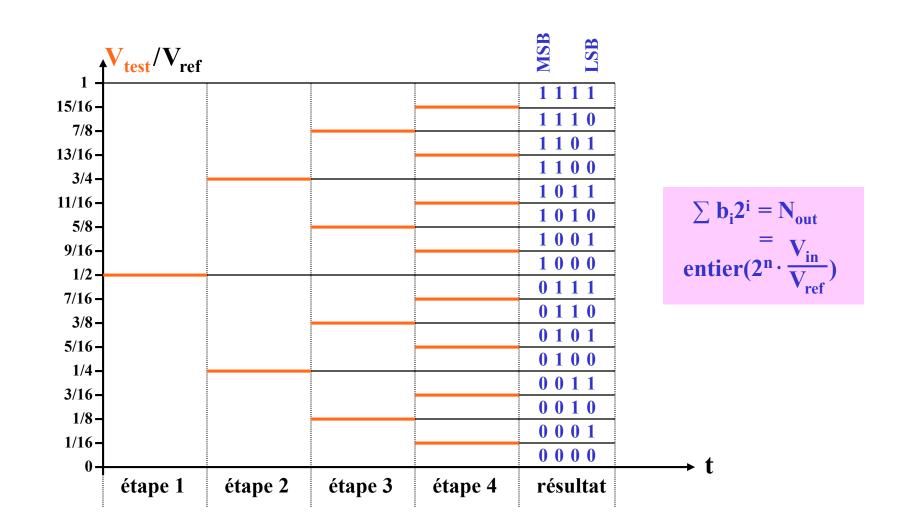

Une logique génère un nombre, codé en binaire, qui est converti en une valeur de test, pour être comparée à  $V_{\rm in}$ . En fonction du résultat: trop grand ou trop petit, la logique génère un nouveau nombre, s'approchant ainsi du résultat final à chaque essai.

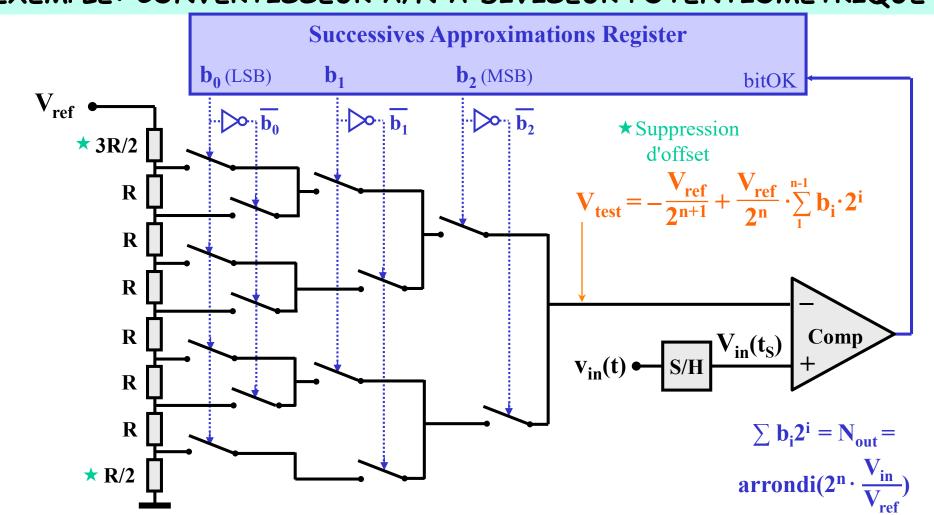

#### EXEMPLE: CONVERTISSEUR A/N A DIVISEUR POTENTIOMETRIQUE

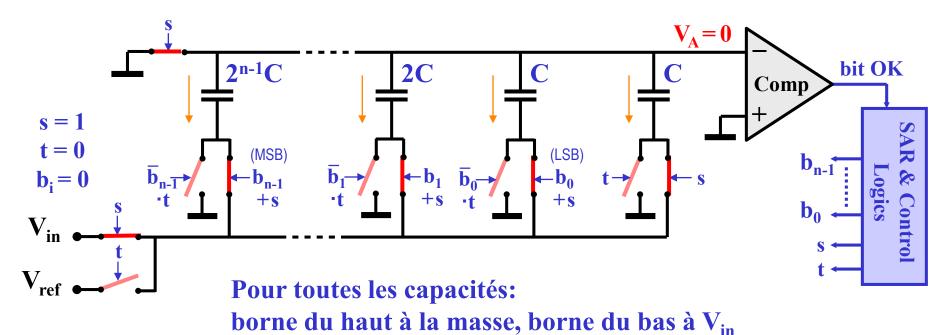

#### CONVERTISSEUR A/N CMOS A CAPACITES PONDEREES

Etape d'échantillonnage de la tension V<sub>in</sub>

Toutes les capacités ont à leurs bornes une tension  $(V_A-V_{in})=-V_{in}$

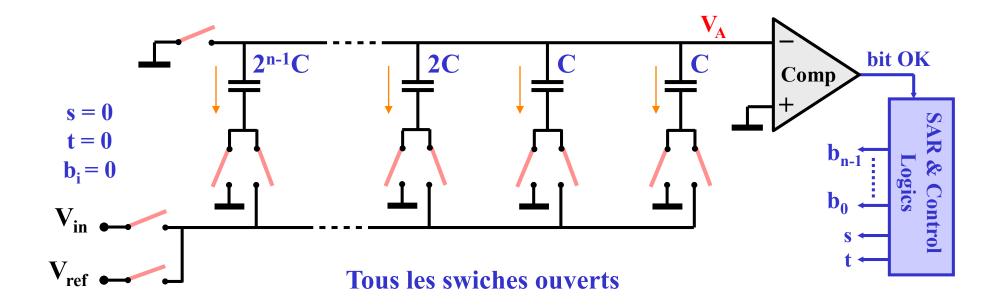

#### CONVERTISSEUR A/N CMOS A CAPACITES PONDEREES

Etape intermédiaire de mémorisation de (- V<sub>in</sub>) sur toutes les capacités

Toutes les capacités gardent à leurs bornes une tension  $(V_A-V_{in})=-V_{in}$ La charge totale stockée vaut  $Q_{tot}=-V_{in}\cdot C\cdot 2^n$

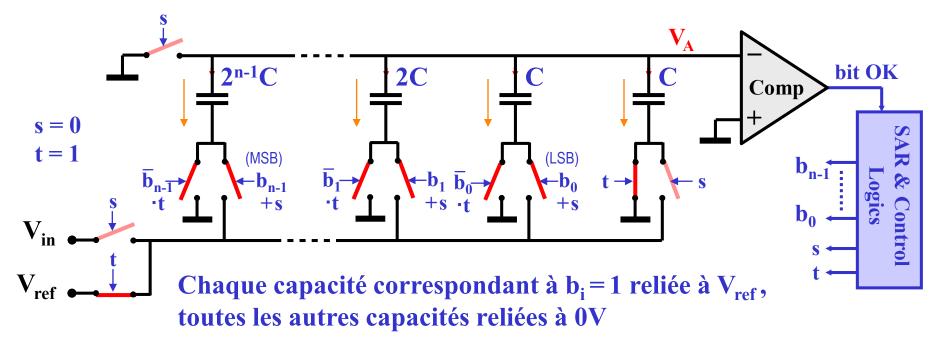

#### CONVERTISSEUR A/N CMOS A CAPACITES PONDEREES

Etape de test, cycles 1 à n: détermination des bits par redistribution de charges

La charge totale stockée reste constante:  $Q_{tot} = -V_{in} \cdot C \cdot 2^n$

$$\mathbf{V_A} = -(\mathbf{V_{in}} - \mathbf{V_{test}})$$

avec  $\mathbf{V_{test}} = \frac{\mathbf{V_{ref}}}{2^n} \cdot \sum_{i=0}^{n-1} \mathbf{b_i} \cdot 2^i$

- CONVERTISSEUR A/N CMOS A CAPACITES PONDEREES

- Convertisseur bien adapté à la technologie CMOS

- Précision limitée essentiellement par la précision des rapports extrêmes des capacités (typiquement 10 bits)

- S/H inhérent au processus

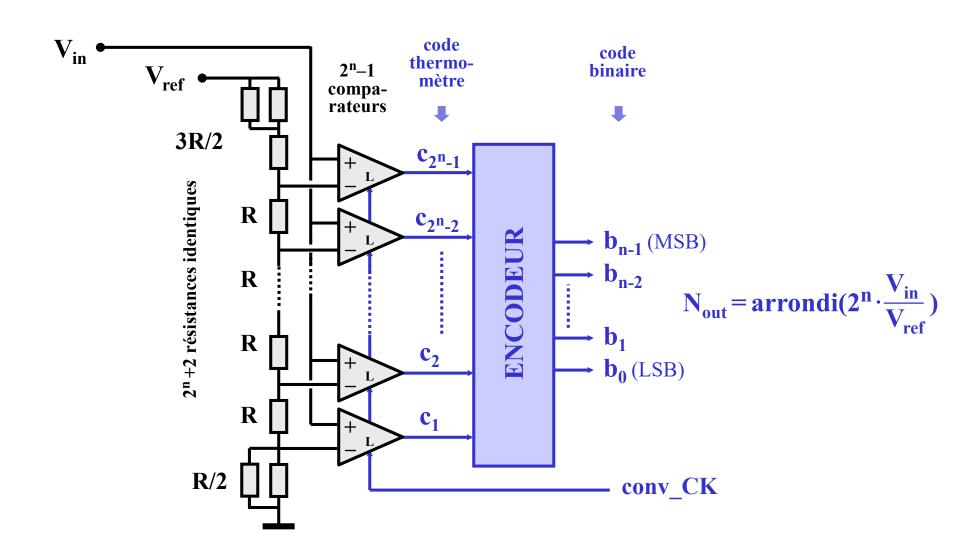

## 3.7. CONVERTISSEURS A/N "FLASH"

### 3.7. CONVERTISSEURS A/N "FLASH"

- Convertisseurs bien adaptés aux technologies tant bipolaire que MOS

- Convertisseurs les plus rapides: la conversion s'effectue en 1 cycle

- Un S&H très rapide à l'entrée améliore encore les performances en HF

- Grand nombre de composants: 2<sup>n</sup>+2 résistances, 2<sup>n</sup>-1 comparateurs, logique à 2<sup>n</sup>-1 entrées et n sorties

- Grande consommation de puissance

- Résolution typiquement limitée à 8 bits